马上注册,看完整文章,学更多FPGA知识。

您需要 登录 才可以下载或查看,没有帐号?立即注册

x

温馨提示:明德扬2023推出了全新课程——逻辑设计基本功修炼课,降低学习FPGA门槛的同时,增加了学习的趣味性,并组织了考试赢积分活动

【问题24】在明德扬提供的SIGNALTAP练习中,找到错误后,要如何修改?

答:明德扬提供的SIGNATAP练习,为了不让学员看到答案,专心找BUG,特意将有错误的代码封装成IP核的形式,即QXP格式文件。

该格式文件的内容是不可观看的。所以这些练习只要找到错误即可,不必修改。

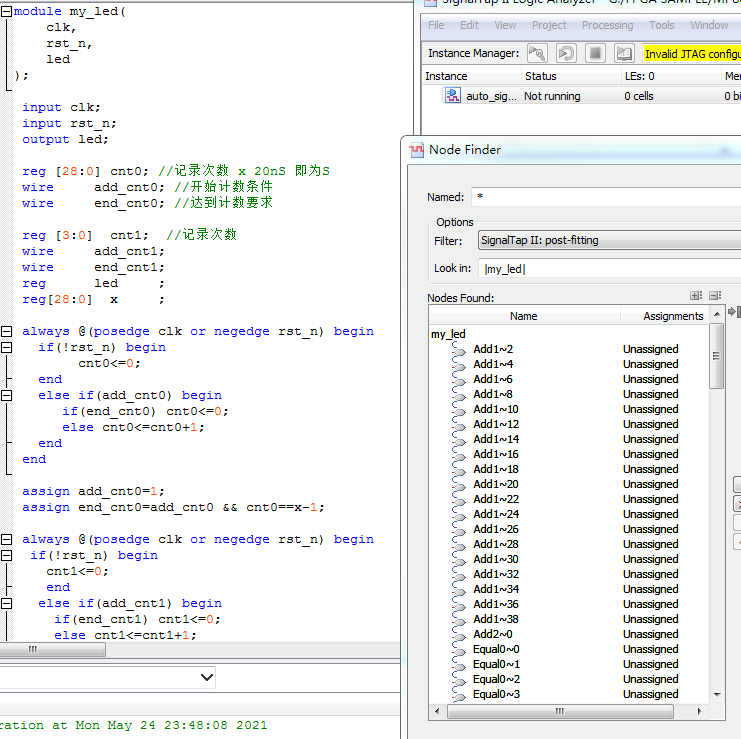

【问题25】在抓取信号时,信号名后面都加有数字,跟我命名的不同,这是为什么?例如 定义中没有Add1,怎么在Nodes Found中有Add1~2.add~4

答:QUARTUS或者VIVADO会对代码进行综合,即变成电路。在进行综合变成电路的时候中,工具会自动产生很多信号来命名每个电路线。所以这是正常的现象。

甚至原有的信号也会改变(如会加数字,会加reg等),所以在看信号的时候,要仔细观察,不用太在意后续。

当然,多尝试抓几次就好。

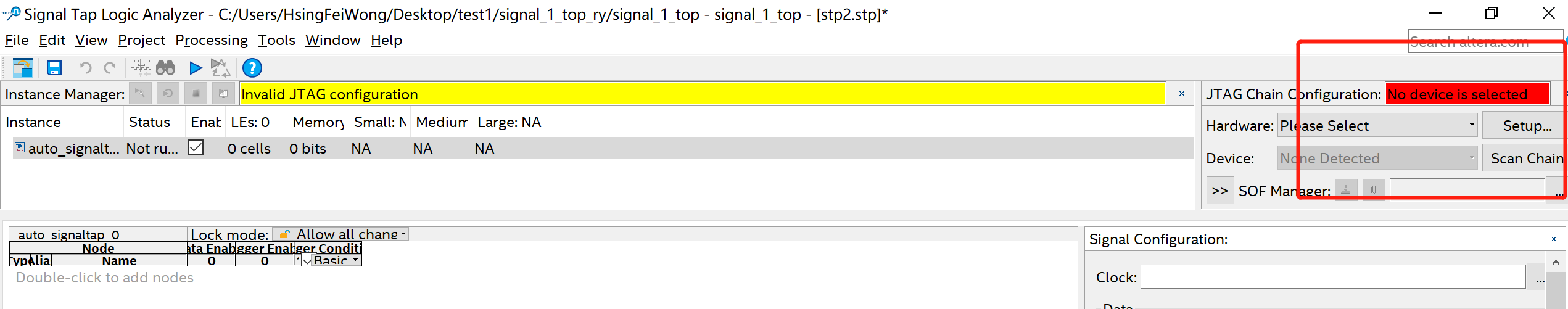

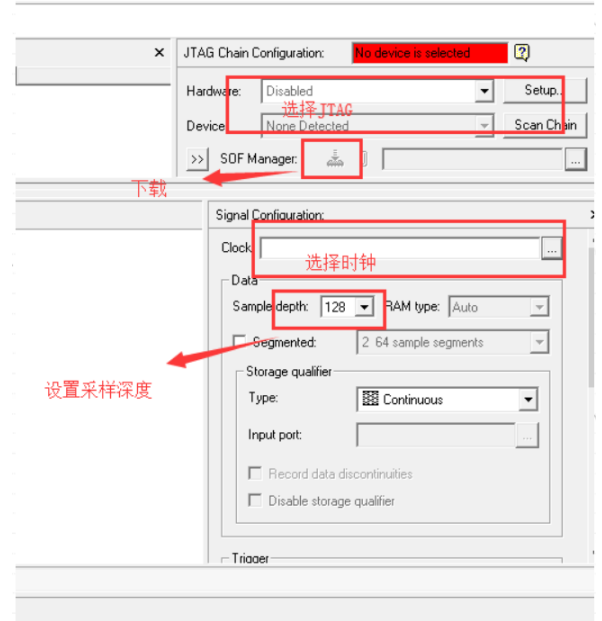

【问题26】quartus开发平台,在做SIGNALTAP 练习中,右窗口提示no device is selected,如下图,请问如何解决?

答:

1.连接好硬件后,请点击hardware旁边的下拉接口,选择USB-Blaster即可。

2.如果问题依旧,是硬件没有连接好或者连接错误,请看http://old.mdy-edu.com/plus/view.php?aid=1191此贴问题3,排除原因。

3.以上两个操作没有解决,请联系服务老师

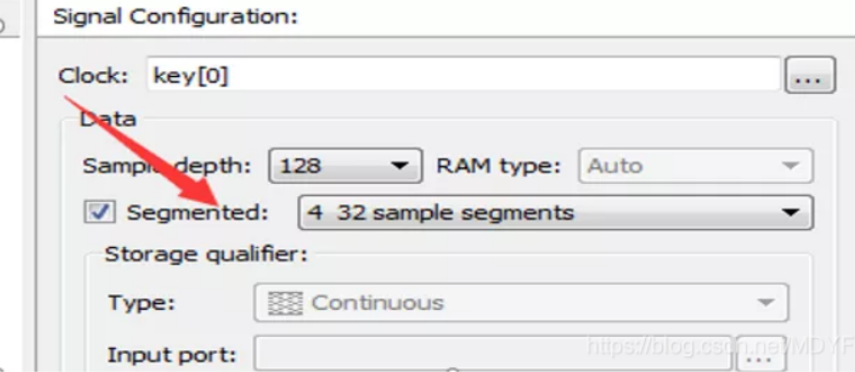

【问题27】请问 SIGNALTAP怎么选择采样时钟?

答:1、SIGNALTAP的采样时钟,不一定是时钟信号,可以是其他任意的信号。总之,SIGNALTAP会在采样时钟的上升沿去捕捉信号的值,

如果没有上升沿,则会一直等待。例如下图所示,就是以按键信号key【0】为采样时钟。在key【0】由0变1时,就会采样一个值。

2、若该工程使用到几个模块,并且每个模块的时钟不一定相同,则我们选择采样时钟时,要根据我们要测试的信号所在的模块的时钟是什么。

【问题28】怎么选择触发条件的次数? 下图所示,通过设置segmented,可以检查满足触发条件的次数。例如,发现按键有时候失灵的情况,为了定位此问题,我想检查按键按下的次数,是否与捕捉到信号次数一致。

答:主要设置为: 1. 把segmented设置为32; 2. 把捕捉到信号key_vld拉到显示窗口,该信号为1表示捕捉到一个按键; 3. 设置触发条件为:key_vld的上升沿; 4. 按下run键,等待触发条件满足; 5. 按下按键4次;按停止捕捉键 。

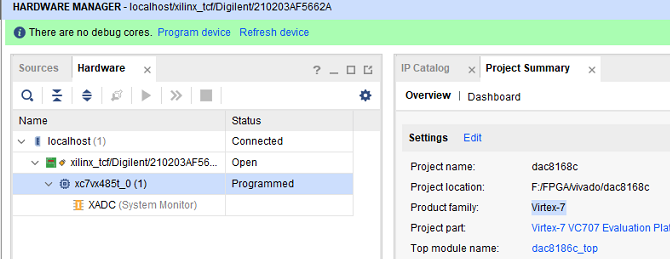

【问题29】如下图所示,当加载比特流文件后,没有显示逻辑分析义的窗口,或者窗口没有波形显示?

答:1. 请确认添加了逻辑分析仪观察的信号。可以通过例化ILA方式添加,也可以通过MARK DEBUG方式添加。

2. 请检查添加逻辑分析仪观察信号,步骤是否正确。

3. 请确认逻辑分析仪的观察时钟正确。要确保上电的时候,就有时钟(最好是晶振产生的时钟)。可以尝试换一下时钟看看

【问题30】请问SignalTap添加时钟,配置JTAG下载怎么操作?

答:添加时钟,配置JTAG下载,在此界面中可以直接下载

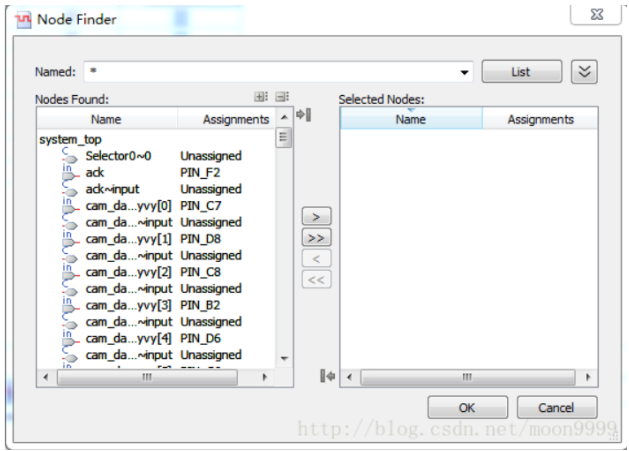

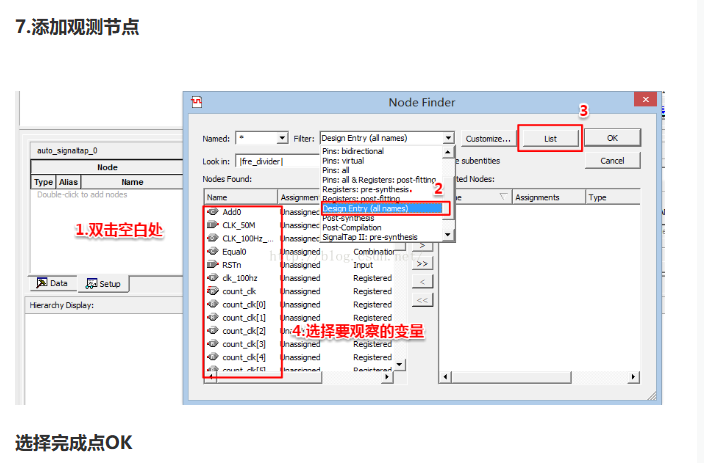

【问题31】如何新建Instance中添加观测节点?

答:在新建Instance中添加观测节点(Nodes)。在Edit菜单中选择Add notes(或者在信号那一大片区域处双击鼠标),弹的Nodes Finder界面,在Named一栏中填入节点名称,

可以用*号通配符;点击List按钮后的箭头,在其中选取信号类型,之后点击list按钮,Nodes Found窗口中将列出查找到的信号,双击以选取所需信号。

用同样的方法加入其它所需信号,完成后点击OK。

【问题32】使用在线调试工具(SIGNALTAP ILA)时,如果修改或者添加信号后,功能由正常变成不正常(或者由不正常变成正常),是什么原因?

关键词:SIGNALTAP ILA,正常变不正常,不正常变正常

答:在线调试工具使用时,会影响到内部信号的时序,有可能出现时序违例的情况。这通常发生在时序约束很紧张的时刻。最好的方法是优化时序,如流水线打拍方式。

另外,不排除原来逻辑功能就有问题,只是刚好暴露而已,建议还是要找到问题点。

【问题33】请问sigaltap采样时钟频率是不是有上限?我用400M的采样时钟采集信号一直触发不到,sigaltap采样时钟速率有没有上限?有的话是多少?

答:

1、采样时钟频率,跟FPGA内部的其他时钟一样,不能任意大的频率,而是应该要满足时序要求的频率。

2、参考《在线调试工具》【问题1】 解答:可能的原因如下:1.该时钟确实是没有,即一直为0,或者一直为1。2. 该clk不是本模块产生的,而是其他模块产生,然后在此模块使用。

这个时候有可能不能作为采样时钟。正确的做法,哪个模块产生的就使用那个模块的信号。例如常见的PLL的C0,C1等。

3、参考《在线调试工具》【问题12】解答。

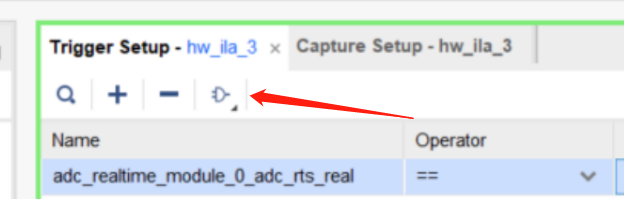

【问题34】在ILA的窗口中,能否设置触发条件为:一个多位数据的某一位为1或者为0?例如信号a[15:0],捕捉a[10]为1。

答:可以的。在触发设置窗口中添加该数据,然后设置为二进制显示,在数值中,不关心的位设置为X,关心的位设置为1或者0即可。例如,信号a[15:0],捕捉a[10]为1,该值可为xxxx_x1xx_xxxx_xxxx。

【问题35】在ILA的窗口中,能否设置触发条件为:一个多位数据的某两位,其中某一位为1来触发?例如信号a[15:0],捕捉a[10]为1,或者a[9]为1。

答:可以的。在触发设置窗口中添加该数据,添加两次,均二进制表示。其中第1个值可为xxxx_x1xx_xxxx_xxxx。第2个值设置为xxxx_xx1x_xxxx_xxxx。尤其注意, 下图要选择“或”的关系。

【问题36】问:在上板调试(如ILA、CHIPSCOPE或者SIGNALTAP等工具)的时候,状态机跳转到不可能的状态,例如同时进入两个不同的状态,从分析上是不可能出现的,偏偏出现了。

答:通常状态机会按代码的逻辑进行跳转。当出现了不可能的状态时,一般是由于亚稳态等原因导致的。亚稳态可能是由于异步信号、时序不满足等原因,请仔细检查。

【问题37】问:如何将某一个变量加入到signtap中呀

答:

【问题38】在线调试生成那个stp文件,如何编译就报错,只有把stp文件删了才正常

答:可以检查下路径里是否包含了中文字符,出现这种情况一般是路径有中文字符

温馨提示:明德扬除了培训学习还有项目承接业务,擅长的项目主要包括的方向有以下几个方面:

1. MIPI视频拼接

2. SLVS-EC转MIPI接口(IMX472 IMX492)

3. PCIE采集系统

4. 图像项目

5. 高速多通道ADDA系统

6. 基于FPGA板卡研发

7. 前端模拟采集、射频、电荷灵敏前置放大器

需要了解相关信息可以联系:易老师13112063618(微信同号)

明德扬科技教育

|

|手机版|小黑屋|MDYBBS

( 粤ICP备16061416号 )

|手机版|小黑屋|MDYBBS

( 粤ICP备16061416号 )